[camera]MIPI协议之D |

您所在的位置:网站首页 › mipi协议中文版pdf B8 › [camera]MIPI协议之D |

[camera]MIPI协议之D

|

1. D-PHY 简介

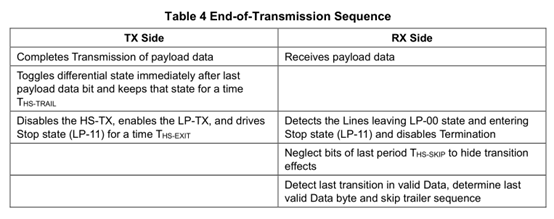

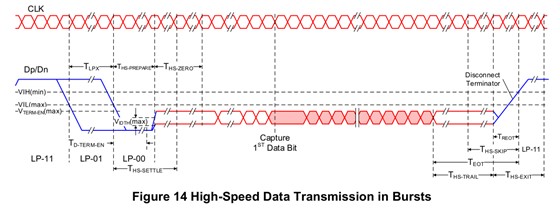

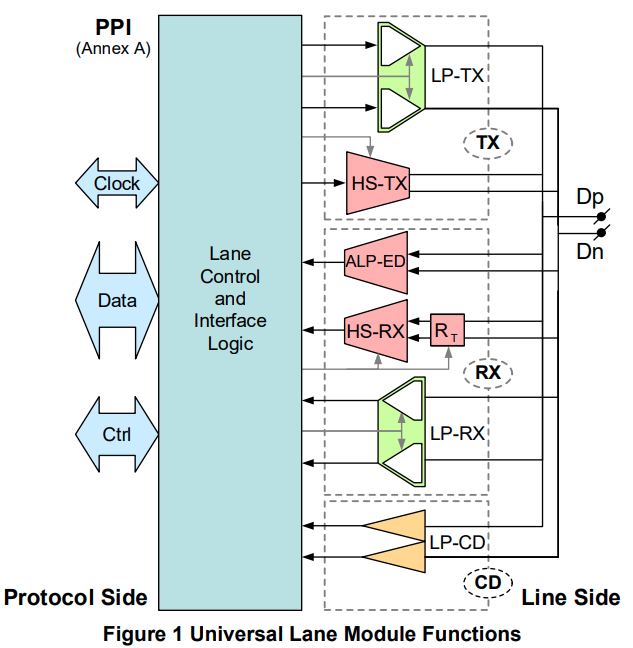

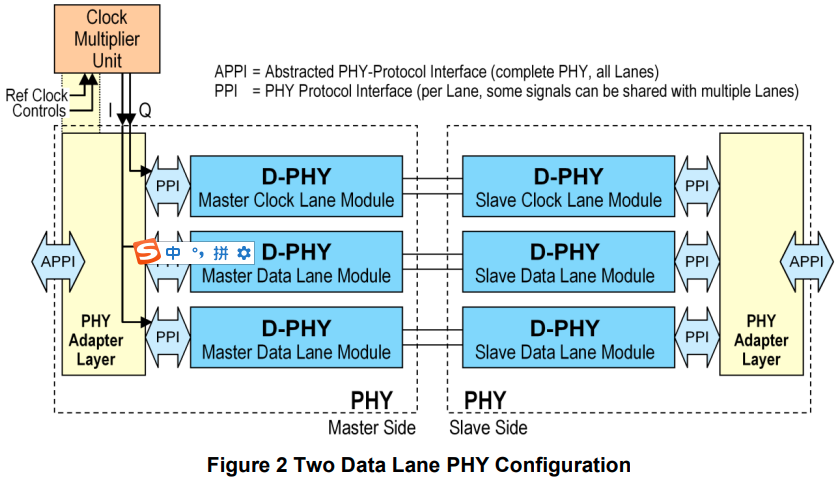

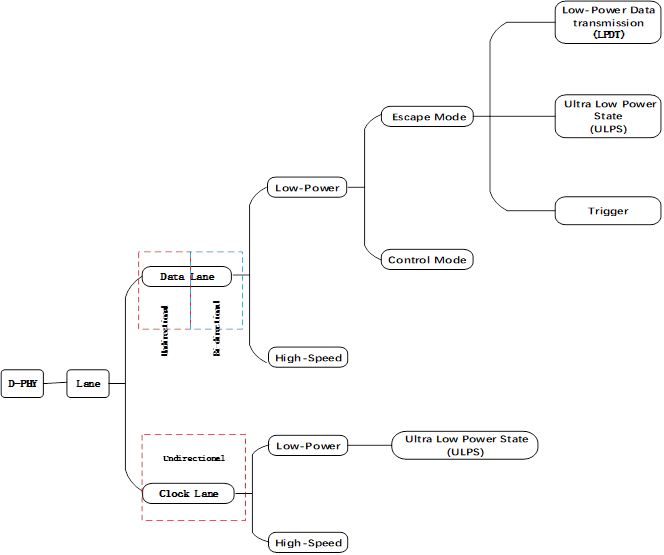

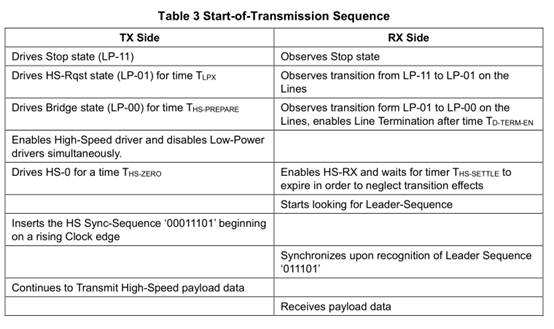

D-PHY由一个Clock Lane和至少一个Data Lane组成,用于在master器件与slave器件之间通信。 时钟信号是单向传输的,由matser到slave;数据可以配置为前向或反向传输。 PHY连接包括高速传输数据的HS Mode(High-Speed Mode)与用于控制的LP Mode(Low-Power Mode)。LP模式下包含许多子模式,其中,Low-Power Escape Mode可以用于低速的异步数据通信。PHY支持LP Mode,也可能支持ALP(Altenate Low Power) Mode,ALP mode用于在long channel的物联网应用场景下替代Low-Power Mode。PHY的实现可能支持ALP Mode与LP Mode之间的切换。 PHY的每条Data Lane使用两条wire,Clock Lane使用两条wire,因此PHY最低配置为4 wires。在HS Mode下,每条Lane由差分信号驱动;LP Mode下,所有wire都是单端且无端接;ALP Mode与HS Mode类似,通信由差分信号实现。 无时滞校准时,传输速率在80至1500Mbps之间;带时滞校准时,传输速率可达2500Mbps;带负载均衡时,传输速率可达4500Mbps。如果反向HS数据传输被实现,由于DPHY的传输不对称性质,反向数据传输速率较低。在ALP Mode下,正向传输速率可达4Mbps,反向传输速率可达1Mbps。LP Mode下的最大数据速率为10Mbps。当时钟频率保持不变时,可以增加Data Lane来提高传输能力。 2. 电气特性介绍 2.1 Lane Module在继续介绍之前,需要明确,Lane由Lane Modules组成,各功能块(function)组成Lane Module,如图所示: HS功能块用于HSDT(High-Speed Data Transmission,高速数据传输)和ALP通信。LP功能块主要用于控制,也可以用于其他功能。I/0功能由Lane Control and Interface Logic块控制,该块与协议交接,决定了Lane Module的全局操作。 HS功能包括差分信号发送器(HS-TX)和差分信号接收器(HS-RX)。 单个Lane Module可能同时配置了HS-TX功能块和HS-RX功能块,两个功能块不会同时工作。当Lane不处于HS Mode时,该功能处于高阻态。 LP功能包括单端发送器(LP-TX),单端接收器(LP-RX),以及LP竞争检测器(LP-CD)。由于LP功能在两条单端线上独立运行,该功能常成对出现。 ALP功能包括能将两条线都置于与参考电平相同的发送器、ALP-ED(ALP Exit Detector, 退出检测器)、信号接收器。 ALP Mode与HS Mode使用同一个HS-TX、HS-RX功能。当PHY支持ALP Mode时,Lane Module提供ALP-ED功能用于退出ALP Mode。 如果包含LP-RX电气功能块的Lane Module上电,那么LP-RX将一直处于激活状态并不断监察Lane电平,直到Lane被配置为ALP Mode。处于ALP Mode时,LP-RX将被关闭,ALP-ED将监察线上电平,直到退出ALP Mode。LP-TX功能块仅在驱动LP状态时启动,LP-CD功能仅用于支持双向操作的LP Mode。LP-CD电气功能块在LP-TX功能块驱动LP States时,检测冲突(ULPS除外)。 在单个Lane Module中无法同时激活LP-TX、HS-TX、HS-RX。为了正常使用,Lane交互连接的双端需要匹配,这意味着一端存在着HS或LP和接收或发送端时,另一端应具备HS或LP的发送或接收端。除此之外,任一结合TX、RX功能和LP Mode的Lane Module都应该具备LP-CD冲突检测功能。而支持ALP Mode的RX Lane Module应具备ALP接收功能。 2.2 主设备和从设备每个连接都有主端和从端。主设备为Clock Lane提供HS DRR时钟信号,并且主设备是主要的数据源。从设备接收Clock Lane上的时钟信号,为主要的数据接收者。主设备到从设备的数据传输路径为前向方向(Forward Direction),相反的方向被称为反向传输。只有双向Data Lane才可以在反向通道上进行传输。在任何情况下,Clock Lane都是前向传输的;可以反转双向Data Lane,从从设备获取数据。 2.3 高频时钟在多种情况下,主控端(Master)需要PLL时钟乘法器产生高频时钟。本文档将产生所需时钟频率的时钟乘法器看作在PHY的架构之外,但在实际使用中该乘法器应集成在PHY内。 2.4 Clock Lane、Data Lane、PPI(PHY Protocol Interface, PHY协议接口)完整的连接除了包括Lane Module之外,还包括连接所有Lane的PHY适配层、时钟乘法单元,以及PHY的协议接口。下图展示了由两个Data Lane、外加一个Clock Lane和时钟乘法单位组成的PHY结构: 所有的Data Lane都支持前向的HS传输和Escape Mode,可能支持ALP Mode。 有两种典型的Data Lane: 双向Data Lane(具有反转(Turnaround)和反向通信的功能)单向Data Lane(不具备反转和反向通信功能) 双向Data Lane应包括以下一项或两项反向通信选项: 高速反向通信(High-Speed Reverse communication)低功耗反向Escape Mode(Low-Power Reverse Escape Mode),包括或不包括LPDT 3. 线上模式Lane的可选模式与Lane类型有关,具体分类如下图所示: MIPI D-PHY通过定义状态码来实现状态转化 Data Lane的正常工作状态为LP Mode和HS Mode,进入HS Mode的方式为发送一个SOT(Start-Of-Transmission Sequence)信号,SOT信号的组成为:  其实是通过发送LP-11引导停止数据发送。 整个高速收发的开始和结束的时序图如下所示: 其实是通过发送LP-11引导停止数据发送。 整个高速收发的开始和结束的时序图如下所示:  在发送端,开始进入 STOP(LP-11),然后通过拉 LP-01、LP-00、HS-0、发送 Sync 字段(HS-00011101)后,不断发送差分数据,直到数据发送完毕。数据发送结束后,退出 High-Speed 模式,再次进入 Stop State。

3.2.2 双向传输Data Lane Turnaround 在发送端,开始进入 STOP(LP-11),然后通过拉 LP-01、LP-00、HS-0、发送 Sync 字段(HS-00011101)后,不断发送差分数据,直到数据发送完毕。数据发送结束后,退出 High-Speed 模式,再次进入 Stop State。

3.2.2 双向传输Data Lane Turnaround

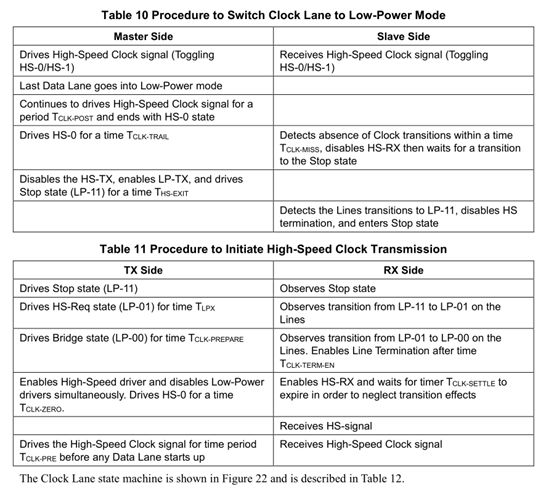

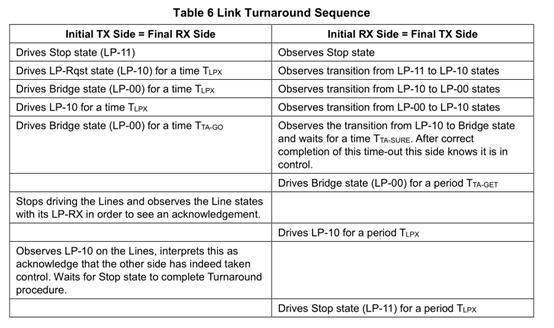

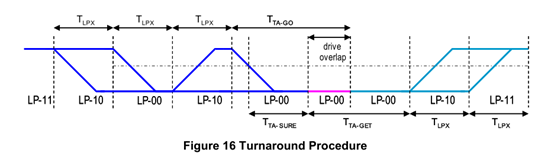

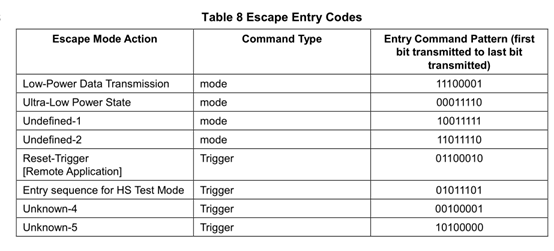

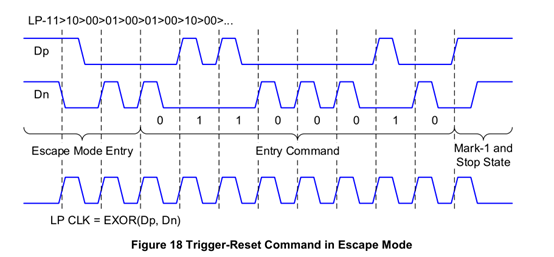

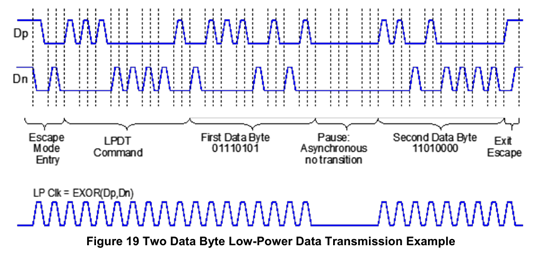

具备双向传输的Data Lane在实现反向传输时,需要进行翻转操作(Turnaround),具体流程如下: Data Lane针对Escape Mode又细分为几类,分别为: LPDT(Low-Power Data Transmission ),在 LP 模式下进行数据传输; ULPS(Ultra-Low Power State),超低功耗状态; Trigger ,用于触发 Reset; 他们都预留了一些内容,来适应以后的标准升级。 3.2.3.1 进入Escape ModeLane通过Escape Mode Entry进入Escape Mode,该过程的流程为LP-11、LP-10、LP-00、LP-01、LP00。进入Escape Mode下子模式的流程为 LP-11、LP-10、LP-00、LP-01、LP-00、[Entry Command],Entry Command编码为: 结合Table 8,进入该模式的时序为: 在该模式下,Lane可以实现低速传输,也可以暂停数据发送: Clock Lane可以抽象为单端的高速差分信号,没有Escape Mode,但有ULPS模式。 3.3.1 Clock Lane High-Speed And Low-PowerClock Lane进入LP Mode与HS Mode流程如下表所示: MIPI标准针对Clock Lane没有定义Escape Mode,但其定义了ULPS,进入方式为:LP-11、LP-10、LP-00 3.4 CD(Contention Detection, 争用监测)在给定的时间段内,正常情况下,连接的两端只有一方驱动线上信号;当两端都不驱动线上信号或同时驱动线上信号时,这种情况为争用(Contention)。 具备双向通信的LP Lane,都必须具备Contention Detection的能力。并检测以下冲突: Lane Module两端同时反向驱动wireLane Module一端驱动一条线为LP-high,另一端驱动这条线为LP-low 上述第一种情况,能被LP-TX和LP-RX一起监测到;第二种情况能被LP-RX监测到。 Pony配置 96712输出配置为2x4-lane意味着,2个CSI接口,每个CSI接口配置了4个图1所示的Lane Module 参考资料 MIPI D-PHY Specification v2.5MIPI协议之D-PHY协议详解MIPI 打怪升级之D-PHY篇 |

【本文地址】

今日新闻 |

推荐新闻 |

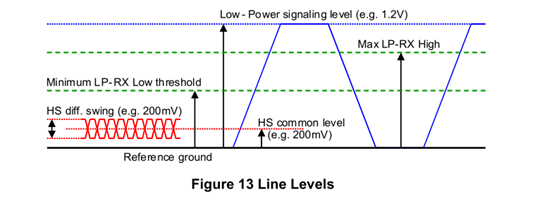

组成PHY的Data Lane与Clock Lane通过两条wire与另一端的对应部分通信。 HS为差分信号传输,信号电平在100mV ~ 200mV之间,电压摆幅在200mV左右;LP信号下,两根wire是独立的信号,不具有差分意义,为单端传输,信号电平在0V~1.2V之间,电压摆幅在1.2V左右。

组成PHY的Data Lane与Clock Lane通过两条wire与另一端的对应部分通信。 HS为差分信号传输,信号电平在100mV ~ 200mV之间,电压摆幅在200mV左右;LP信号下,两根wire是独立的信号,不具有差分意义,为单端传输,信号电平在0V~1.2V之间,电压摆幅在1.2V左右。

逻辑上,单个Lane的PPI是指完成该Lane功能的信号合集。图2中的时钟信号是由所有Lane共用,时钟乘法单元的参考时钟和控制信号未在图中描述。

逻辑上,单个Lane的PPI是指完成该Lane功能的信号合集。图2中的时钟信号是由所有Lane共用,时钟乘法单元的参考时钟和控制信号未在图中描述。

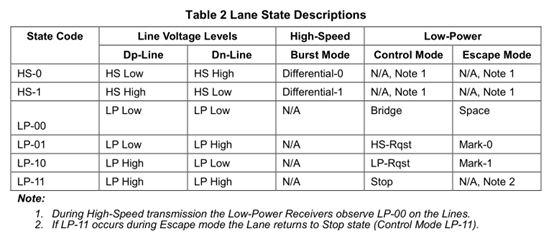

HS-0:表示High-Speed模式下,Dp那根线的数据是0,由于High-Speed是差分信号,那么Dn就是1。 HS-1:表示High-Speed 模式下, Dp那根线的数据是1,由于High-Speed是差分信号,那么Dn就是0。 在Low-Power模式下,Lane的2根线是独立的,不代表差分信号,那么2根线就有4种表达方式: LP-00:表示在Low-Power模式下,Dp那根线的数据是0,Dn那根线的数据是0。 LP-01:表示在Low-Power模式下,Dp那根线的数据是0,Dn那根线的数据是1。 LP-10:表示在Low-Power模式下,Dp那根线的数据是1,Dn那根线的数据是0。 LP-11:表示在Low-Power模式下,Dp那根线的数据是1,Dn那根线的数据是1

HS-0:表示High-Speed模式下,Dp那根线的数据是0,由于High-Speed是差分信号,那么Dn就是1。 HS-1:表示High-Speed 模式下, Dp那根线的数据是1,由于High-Speed是差分信号,那么Dn就是0。 在Low-Power模式下,Lane的2根线是独立的,不代表差分信号,那么2根线就有4种表达方式: LP-00:表示在Low-Power模式下,Dp那根线的数据是0,Dn那根线的数据是0。 LP-01:表示在Low-Power模式下,Dp那根线的数据是0,Dn那根线的数据是1。 LP-10:表示在Low-Power模式下,Dp那根线的数据是1,Dn那根线的数据是0。 LP-11:表示在Low-Power模式下,Dp那根线的数据是1,Dn那根线的数据是1 顺序设置:

顺序设置: 时序如下:

时序如下:  Note:即便是翻转了,Master与Slave身份并不互换。

Note:即便是翻转了,Master与Slave身份并不互换。

可以看到,在传输第一个字节后, 停顿一段时间后,进行第二个字节的传输。

可以看到,在传输第一个字节后, 停顿一段时间后,进行第二个字节的传输。